从原理到实践 详解MOS管驱动电路在集成电路中的设计方法

MOS管(金属氧化物半导体场效应晶体管)是现代集成电路的核心开关元件,其驱动电路的设计质量直接决定了系统的效率、速度和可靠性。在集成电路设计中,MOS管驱动电路并非简单的连接,而是一个需要综合考虑电气特性、布局布线和系统需求的精密环节。

一、核心设计原则与要求

- 提供足够的驱动能力:驱动电路必须能为MOS管的栅极电容(Cgs、Cgd)提供足够大的充放电电流,以确保快速开关,减少开关损耗。驱动电流不足会导致开关速度慢,损耗增加甚至发热损坏。

- 确保合适的栅极电压:

- 开启电压:必须提供高于MOS管阈值电压(Vth)且足够高的电压(通常为10-15V或根据工艺确定),使其完全进入低阻态(导通)。

- 关断电压:通常需要将栅极电压拉低至0V或负压,以确保可靠关断,防止因米勒效应等引起的误导通。

- 实现快速开关与抑制振荡:通过优化驱动电阻和布局,在追求速度的抑制由寄生电感和电容引起的栅极振荡和电压过冲。

- 提供隔离与保护:在高压或浮地应用中,常需要隔离驱动(如使用电平移位器、隔离变压器或电容隔离)。还需集成欠压锁定、过流保护、死区时间控制等功能。

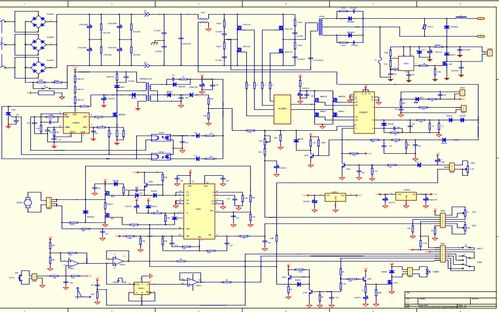

二、集成电路中MOS管驱动电路的基本架构与原理图设计

在IC设计中,驱动电路通常作为功率器件(如Power MOSFET)的配套模块集成在同一芯片上,或作为独立的驱动IC。其典型原理图核心部分包括:

- 输入级与电平移位:

- 接收来自低压控制逻辑(如3.3V或5V CMOS)的PWM信号。

- 若驱动高压侧MOS管(在半桥、全桥拓扑中),则需要电平移位电路。常见设计采用高压电平移位器或自举电路(Bootstrap)。自举电路通过一个二极管和电容,在低压侧开关管导通时为高压侧驱动电路提供浮动电源。

- 控制与保护逻辑:

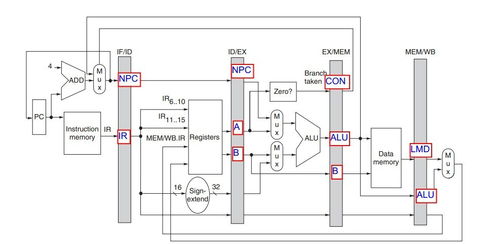

- 死区时间插入:通过数字延迟电路,确保上下管不会同时导通,防止直通短路。

- 欠压锁定:监测驱动电源电压,低于阈值时强制关闭输出,防止MOS管因驱动不足而工作在线性区发热。

- 输出级(核心功率放大级):

- 这是驱动能力的直接体现。通常采用推挽输出结构(图腾柱结构)。

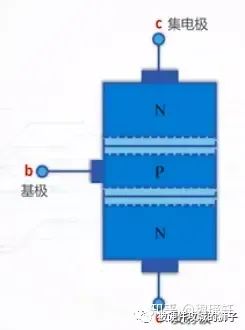

- 上拉管(PMOS或PNP):负责向栅极快速充电(拉高电压)。

- 下拉管(NMOS或NPN):负责从栅极快速放电(拉低电压)。

- 设计要点:

- 上拉和下拉管的尺寸(W/L)需要精心设计,以提供所需的峰值源电流和灌电流。

- 为了进一步优化开关过程,有时会采用非对称驱动,即开启和关断速度可独立调节。

- 栅极电阻集成:

- 在IC内部,可以集成一个小的栅极电阻(Rg),或通过控制输出级晶体管的导通电阻来实现等效电阻,用以抑制振荡和调节dv/dt。外部通常仍会预留引脚连接可调电阻,以适配不同的应用场景。

三、集成电路版图设计的关键考量

原理图设计完成后,版图实现至关重要:

- 电流路径与布线:输出级的大电流路径必须宽而短,以减小寄生电阻和电感。电源和地的布线需要低阻抗。

- 隔离与噪声:

- 高压电平移位部分与低压控制部分之间需要有足够的物理隔离(如深N阱、隔离环),防止闩锁和噪声耦合。

- 驱动电路的电源和地应尽可能与敏感的模拟/数字电路分开,采用星型接地或单独引脚。

- 热设计:驱动电路本身,尤其是输出级,也会有功耗。需要合理分布有源区,并考虑热耦合,避免局部过热。

- ESD保护:所有对外的输入/输出引脚必须集成有效的静电放电保护电路。

四、设计流程与验证

- 系统规格定义:明确驱动的电压、电流能力、开关频率、上升/下降时间、死区时间、保护功能等。

- 电路设计与仿真:

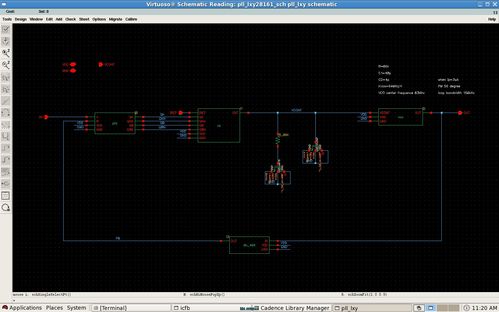

- 使用EDA工具(如Cadence Virtuoso)进行晶体管级原理图设计。

- 进行直流、瞬态、工艺角、蒙特卡洛等仿真,验证在所有工作条件下(不同电压、温度、工艺偏差)的功能和性能。

- 特别关注开关波形、驱动电流、功耗和潜在振荡。

- 版图实现与后仿真:

- 绘制版图,严格遵守设计规则。

- 提取包含寄生参数的网表(RC Extraction),进行带寄生的后仿真。这是确保实际芯片性能与原理图仿真一致的关键步骤,寄生效应会显著影响高速开关性能。

- 流片与测试:制作原型芯片,在实验室中实测其驱动真实MOS管负载的性能。

###

MOS管驱动电路在集成电路中的设计,是一个融合了器件物理、模拟电路设计、数字逻辑和版图艺术的系统工程。优秀的驱动设计能够充分释放功率MOS管的潜力,提升整个电源或电机控制系统的效率、功率密度和可靠性。随着工艺进步,将更多驱动、保护、诊断功能智能地集成于单芯片,是现代功率集成电路发展的核心趋势。

如若转载,请注明出处:http://www.mytouchtime.com/product/70.html

更新时间:2026-02-24 01:50:06