集成电路设计中的关键电路保护方法与策略

在集成电路设计中,电路保护是确保芯片在各种工作条件下稳定、可靠运行的关键环节。随着工艺尺寸的不断缩小和系统复杂度的提高,对电路保护的需求也日益增强。有效的保护设计能防止芯片因过压、过流、静电放电、闩锁效应等异常情况而损坏,从而提升产品的可靠性和寿命。以下是集成电路设计中一些核心的电路保护方法。

1. 静电放电(ESD)保护

静电放电是集成电路在制造、测试、运输和使用过程中最常见的威胁之一。ESD保护电路通常集成在芯片的输入/输出(I/O)引脚和电源引脚上,其设计目标是快速泄放静电电荷,防止内部电路受损。常见方法包括:

- 基于二极管的保护结构:利用正向导通和反向击穿特性,将ESD电流引导至电源或地线。

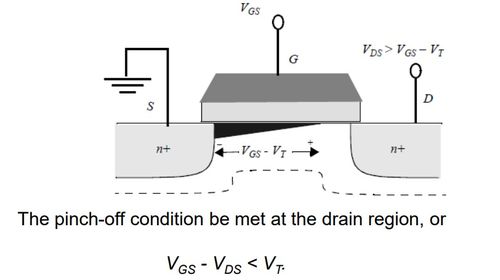

- RC触发的栅极接地NMOS(GGNMOS):在ESD事件发生时,通过RC网络触发NMOS导通,形成低阻抗放电路径。

- 全芯片级保护:在电源域之间设计钳位电路,如电源钳位(Power Clamp),防止电源电压尖峰。

2. 闩锁效应(Latch-up)防护

闩锁效应是由寄生双极晶体管形成的正反馈回路导致的低阻抗状态,可能引发芯片烧毁。防护措施包括:

- 增加衬底和阱的接触密度:通过添加更多接触孔,降低寄生电阻,抑制触发电流。

- 使用保护环(Guard Ring):在敏感电路周围布置P+和N+扩散区,隔离噪声和载流子注入。

- 优化布局间距:根据工艺设计规则,合理安排NMOS和PMOS的距离,减少寄生效应。

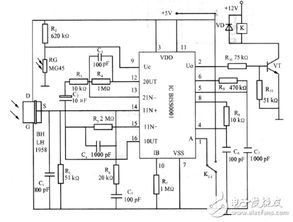

3. 过压与过流保护

在电源管理或接口电路中,电压或电流的异常波动可能损坏器件。设计方法包括:

- 电压钳位电路:例如齐纳二极管或MOSFET基钳位,限制引脚电压不超过安全范围。

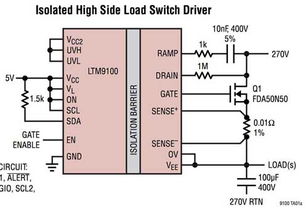

- 电流限制电路:通过检测电流并反馈控制驱动管,防止短路或过载,常见于功率输出级。

- 欠压锁定(UVLO)和过压保护(OVP):在电源模块中集成,确保芯片仅在安全电压范围内工作。

4. 热保护

高温会加速器件老化甚至失效。热保护通常通过温度传感器实现:

- 集成热关断电路:当芯片温度超过阈值时,自动关闭部分或全部电路,待冷却后恢复。

- 动态热管理:根据温度调整时钟频率或电源电压,减少功耗和发热。

5. 电磁干扰(EMI)抑制

在高频或混合信号设计中,EMI可能引起噪声和性能下降。保护策略包括:

- 屏蔽与隔离:使用Guard Ring或深阱隔离敏感模拟电路与数字电路。

- 滤波设计:在电源和信号路径中添加RC或LC滤波器,衰减高频噪声。

- 布局优化:减少长走线环路,采用差分信号和对称布局以降低辐射。

6. 工艺角与变异保护

由于制造工艺的偏差,电路参数可能在不同批次或温度下漂移。设计时需考虑:

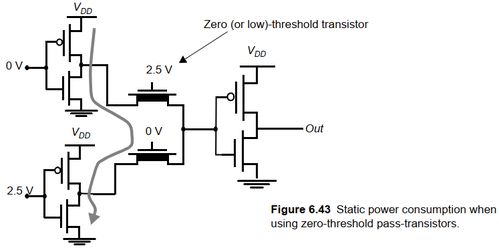

- 稳健的偏置设计:使用带隙基准等稳定电压源,减少工艺和温度影响。

- 自适应校准电路:例如在ADC或PLL中集成校准模块,实时调整参数。

- 多角仿真验证:在设计阶段覆盖极端工艺角,确保保护功能在所有条件下有效。

###

电路保护设计是集成电路开发中不可或缺的一部分,它需要跨学科的知识,涵盖器件物理、电路理论和布局技术。随着先进工艺的发展,保护电路的设计变得更加挑战性,但通过综合运用ESD防护、闩锁抑制、过压过流管理、热控制、EMI抑制和工艺稳健性设计,工程师可以显著提升芯片的可靠性和市场竞争力。在实际项目中,保护电路应与核心功能协同优化,平衡面积、功耗和性能,以实现最佳的整体解决方案。

如若转载,请注明出处:http://www.mytouchtime.com/product/51.html

更新时间:2026-02-28 13:14:33